# Model 5312B 4 Axis Quadrature Encoder - PC

# <u>Hardware Guide</u>

ACS-Tech80 Part Number 700019

Document version no. 1.30

Information deemed to be correct at time of publishing. ACS-Tech80, Inc. reserves the right to change specifications without notice. ACS-Tech80, Inc. is not responsible for incidental, consequential, or special damages of any kind in connection with this document.

Intentionally Left Blank

Document version no 1.30 (May 2001)

Part number: 700019

Microsoft Windows is a registered trademark of Microsoft Corporation.

Changes are periodically made to the information contained in this manual. These changes are published in "software/hardware release notes," and will be incorporated into new editions. This document cannot be reproduced in any form, without permission in writing from ACS-Tech80 Inc. All Rights Reserved.

Copyright © 2000, 2001 ACS-Tech80.

ACS-Tech80 Inc. reserves the right to change specifications without notice.

Internet: <u>http://www.acs-tech80.com/</u> E-mail: <u>info@acs-tech80.com</u> support@acs-tech80.com

#### ACS-Tech80 Inc.

7351 Kirkwood Lane North Suite 130 Maple Grove, MN, 55427, USA Tel: +1.763.493.4080 Fax: +1.763.493.4089

#### ACS-Tech80 Ltd.

Ramat Gabriel Industrial Park, POB 5668 Migdal Ha'Emek, 10500, Israel Tel: +972.6.6546440 Fax: +972.6.6546443

Intentionally Left Blank

# Changes to this Guide

| Version | Date     | Section | Changes                                                                                                                                   | ECR   |

|---------|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.30    | May 2001 | all     | Reformatted entire manual per<br>instructions from Ltd. to conform to new<br>manual style. Many detail changes to<br>improve readability. | R0006 |

|         |          |         |                                                                                                                                           |       |

## Preface

This manual provides instructions and reference information for use with the Model 5312B Quadrature Encoder Board from ACS-Tech80 Inc. The purpose of this manual is to answer basic application questions you may have when working with this card.

ACS-Tech80 assumes that the user of this system possesses some fundamental knowledge of programming and computer systems operation. Such knowledge is required to successfully set up and operate the model 5312B.

ACS-Tech80 will be eager to assist you with setup and application problems pertaining to the model 5312B that are not addressed in this manual. We recommend that you consult documents provided by the manufacturer concerning questions relating to PCs and compilers.

ACS-Tech80 manufactures and markets board—level products and systems for a wide variety of applications involving industrial I/O, link, or interface between a digital computer subsystem and the system.

# **Table of Contents**

| Changes to this Guide                                                                                     | 5  |

|-----------------------------------------------------------------------------------------------------------|----|

| Preface                                                                                                   | 6  |

| List of Tables                                                                                            | 9  |

| List of Figures                                                                                           | 10 |

| About this Manual Set                                                                                     | 11 |

| Quality Control                                                                                           |    |

| Conventions                                                                                               |    |

| Procedural                                                                                                | 11 |

| Notational                                                                                                | 11 |

| Before Installing the Model 5312B                                                                         | 14 |

| Unpacking and Inspection                                                                                  |    |

| Electrostatic Discharge (ESD)                                                                             |    |

| Development Kit                                                                                           | 16 |

| Basic Tools and Test Equipment                                                                            |    |

|                                                                                                           |    |

| 1 Introduction and Installation                                                                           |    |

| 1.1 Description                                                                                           |    |

| 1.2 Technical Specifications.                                                                             |    |

| 1.3 Setting the Jumpers<br>1.3.1 Base Addressing                                                          |    |

| 1.3.2 Indirect Addressing                                                                                 |    |

| 1.3.3 Termination Resistors                                                                               |    |

| 1.3.4 Selecting an Index Option                                                                           |    |

| 1.3.5 Selecting the Card Configuration                                                                    |    |

| 1.3.6 Interrupt Selection                                                                                 |    |

| 1.3.7 Wait States                                                                                         | 33 |

| 1.4 Installation                                                                                          |    |

| 1.4.1 Power Considerations                                                                                |    |

| 1.4.2 Connector Pinouts                                                                                   | 35 |

| 2 Operation and Programming                                                                               | 38 |

| 2.1 Theory of Operation                                                                                   |    |

| 2.2 Programming                                                                                           |    |

| 2.2.1 Writing the Preset Register (PR)                                                                    |    |

| 2.2.2 Reading the Output Latch Register (OL)                                                              |    |

| 2.2.3 Writing the Command Register (CR)                                                                   |    |

| 2.2.4 Master Control Register (MCR).                                                                      |    |

| <ul><li>2.2.5 Input Control Register (ICR)</li><li>2.2.6 Output/Counter Control Register (OCCR)</li></ul> |    |

| 2.2.7 Quadrature Register (OR)                                                                            |    |

| 2.2.8 Output Status Register (OSR)                                                                        |    |

| 2.2.9 Typical Programming Examples                                                                        |    |

| 2.2.10 Selecting A Sample Clock Frequency                                                                 |    |

| 3 Interrupt Control                                                                                       | ۸۵ |

| 3.1 Description of Interrupt Control                                                                      |    |

|                                                                                                           |    |

| 3.1.2 Priority Resolver (PR)                      |    |

|---------------------------------------------------|----|

| 3.1.3 Interrupt Mask Register (IMR)               |    |

| 3.1.4 Interrupt Output (INT)                      |    |

| 3.2 PIC Operation                                 |    |

| 3.2.1 Interrupt Sequence, 80x86/80x88 Mode        |    |

| 3.2.2 End-of-Interrupt Command                    |    |

| 3.2.3 Completing an Interrupt                     |    |

| 3.3 Operating Modes                               |    |

| 3.3.1 Fully Nested Mode                           |    |

| 3.3.2 Special Mask Mode                           |    |

| 3.3.3 Specific Rotation (Specific Priority)       |    |

| 3.3.4 Automatic Rotation (Equal Priority)         |    |

| 3.3.5 Non-Vectored Mode (Poll Command)            |    |

| 3.4 PIC Programming                               |    |

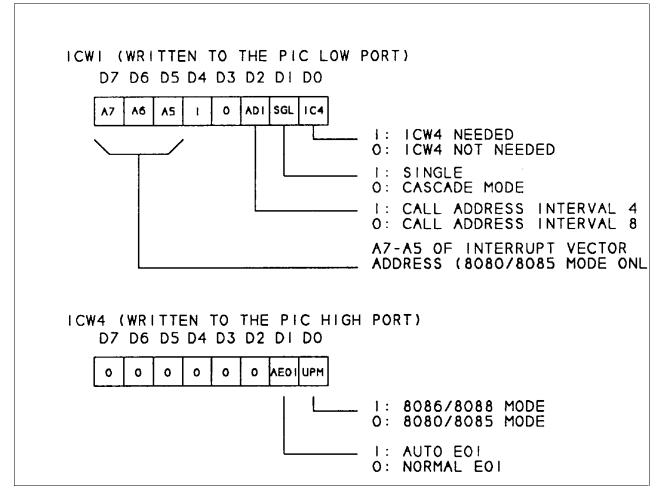

| 3.4.1 Initialization Command Words (ICW)          |    |

| 3.4.2 ICW1 Format and Description                 |    |

| 3.4.3 ICW4 Format and Description                 |    |

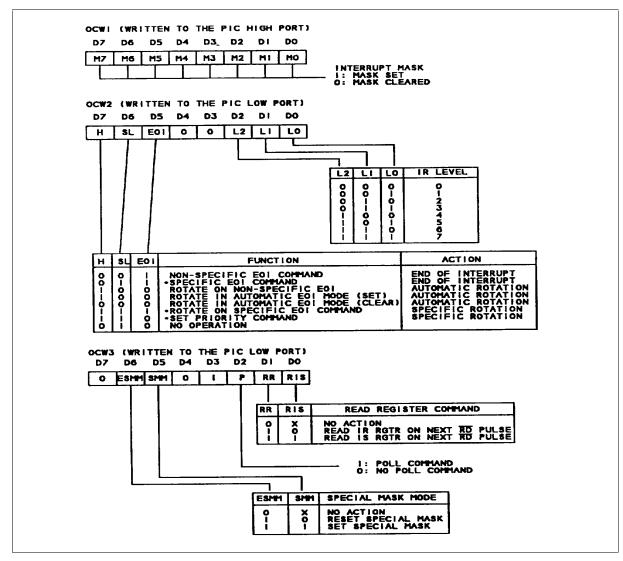

| 3.4.4 Operation Command Words (OCW)               |    |

| 3.4.5 OCW1 Format and Description                 |    |

| 3.4.6 OCW2 Format and Description                 |    |

| 3.4.7 OCW2 Commands                               |    |

| 3.4.8 OCW3 Format and Description                 |    |

| Appendix A - PC I/O and Interrupt Mapping         |    |

| PC I/O Map                                        |    |

| PC Interrupt Map                                  |    |

|                                                   |    |

| Appendix B - Tech Bulletins and Application Notes |    |

| Timer Application in Velocity Mode                |    |

| Setting up Axis 3 as an Interval Timer            |    |

| Appendix C - Outputs & Pinouts                    |    |

| Appendix D - Revision History                     | 66 |

| Revision A                                        |    |

| Revision B                                        |    |

| Revision C                                        |    |

| Revision D                                        |    |

| Revision E                                        |    |

| Revision F                                        |    |

| Revision G                                        |    |

| Revision H                                        |    |

| Revision I                                        |    |

|                                                   |    |

| Appendix E - 5312B Schematics                     |    |

## List of Tables

| Table 1.0 3M® Grounding System Components. 1                           | 15 |

|------------------------------------------------------------------------|----|

| Table 1.1 W19, Base Address Select (upper nibble)                      | 22 |

| Table 1.2 5312 I/O Map 2                                               | 25 |

| Table 1.3 Termination Resistors in Differential Mode   2               | 26 |

| Table 1.4 Termination Resistors in Single-Ended Mode   2               | 26 |

| Table 1.5 Index Option Selections.   2                                 | 29 |

| Table 1.6 Jumper Selection for Differential/Single-Ended Operation   3 | 30 |

| Table 1.7 Sample Clock Frequency Jumper Settings                       | 31 |

| Table 1.8 Cascading the Counters                                       | 31 |

| Table 1.9 Jumpering for Disabling/Enabling Borrow Interrupts   3       | 32 |

| Table 1.10 Selecting an Interrupt                                      | 32 |

| Table 1.11 Generating Wait States                                      | 33 |

| Table 1.12 Connector J1-J4 Pin Assignments                             | d. |

| Table 1.13 Default Jumper settings For All Board Versions              | 36 |

| Table 1.13 Default Jumper settings For All Board Versions (Continued.) | 37 |

| Table 2.1 Register Select 4                                            | 40 |

| Table 2.2 Output/Counter Control Modes.   4                            | 43 |

| Table 2.3 Quadrature Register Modes   4                                | 14 |

| Table 3.1 Interrupt Code 5                                             | 52 |

| Table A.1 PC I/O Map                                                   | 51 |

| Table A.2 PC Interrupt Map6                                            | 32 |

# List of Figures

| Figure 1 A typical ESD workstation                                           |

|------------------------------------------------------------------------------|

| Figure 1.1 Functional block diagram for the 5312 20                          |

| Figure 1.2 Jumper locations for the 5312                                     |

| Figure 1.3 Encoder termination resistor locations                            |

| Figure 1.4 LED locations on the card edge                                    |

| Figure 1.5 Connector locations on the board                                  |

| Figure 2.1 Example of a 4-stage signal conditioning filter                   |

| Figure 3.1 PIC block level diagram                                           |

| Figure 3.2 PIC initialization sequence                                       |

| Figure 3.3 PIC ICW format                                                    |

| Figure 3.4 PIC OCW format. Write to the OCW at any time after initialization |

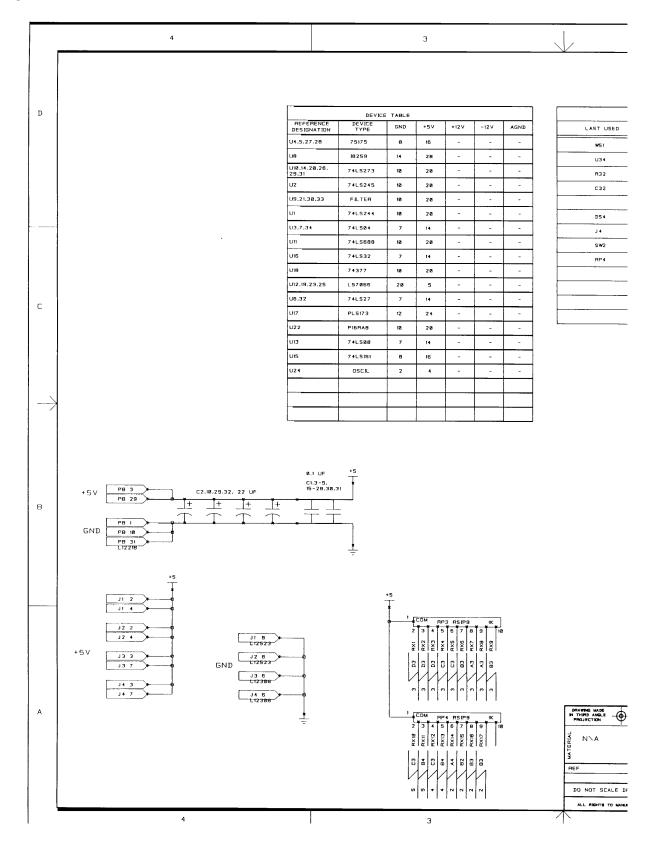

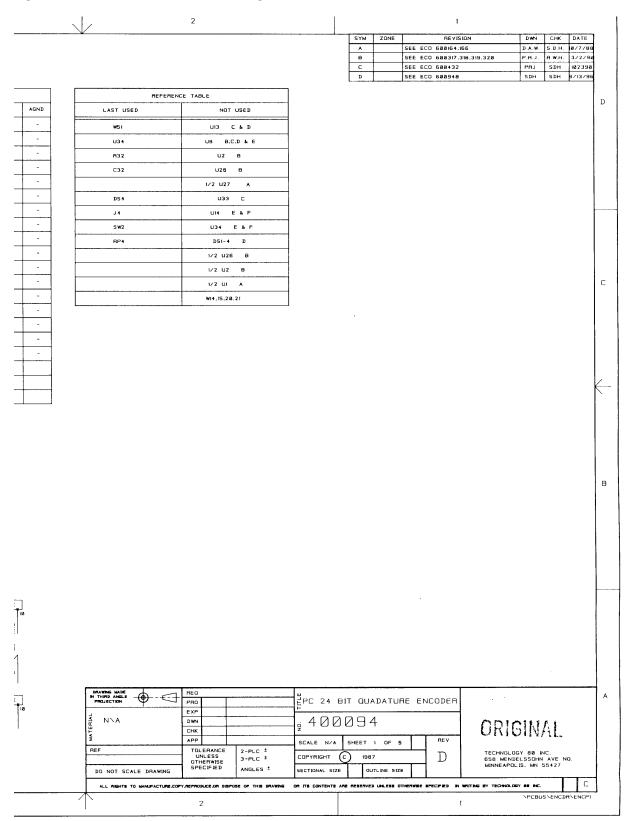

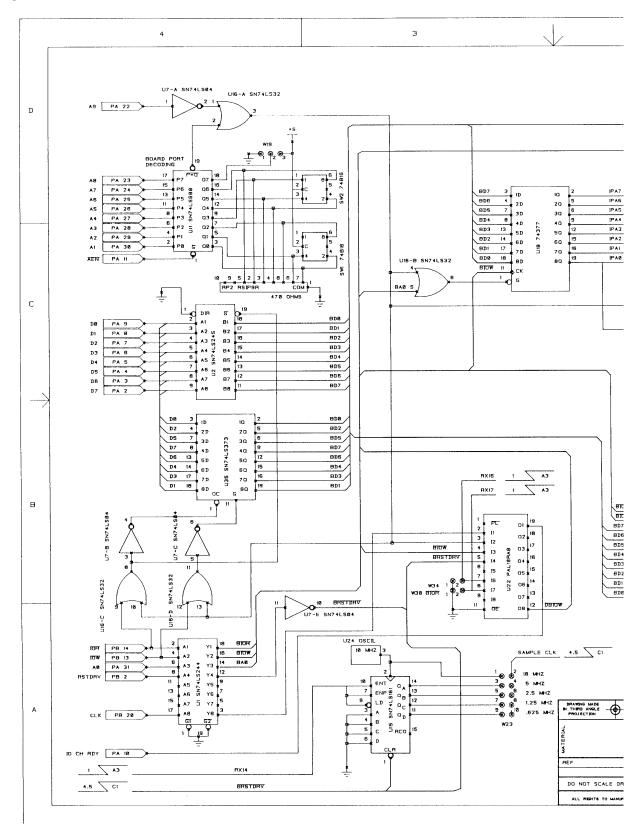

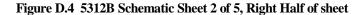

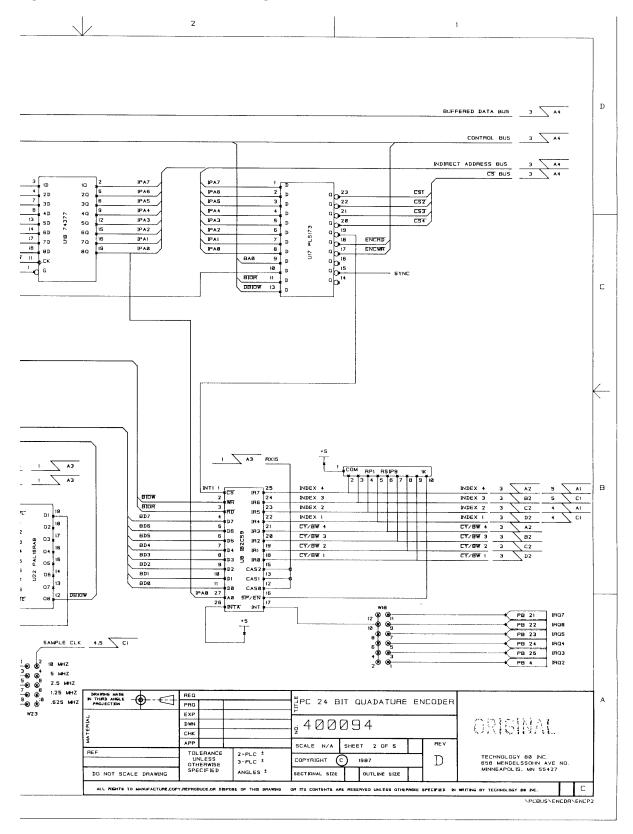

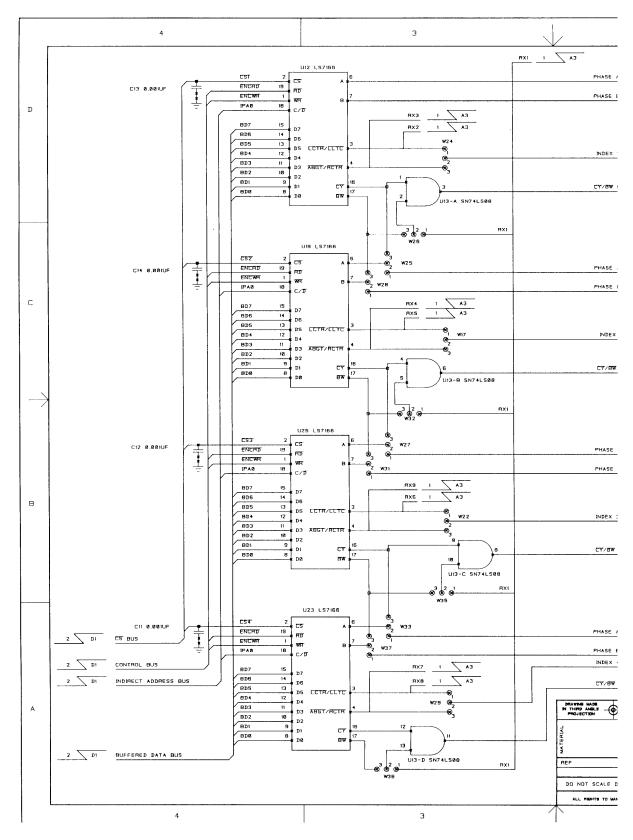

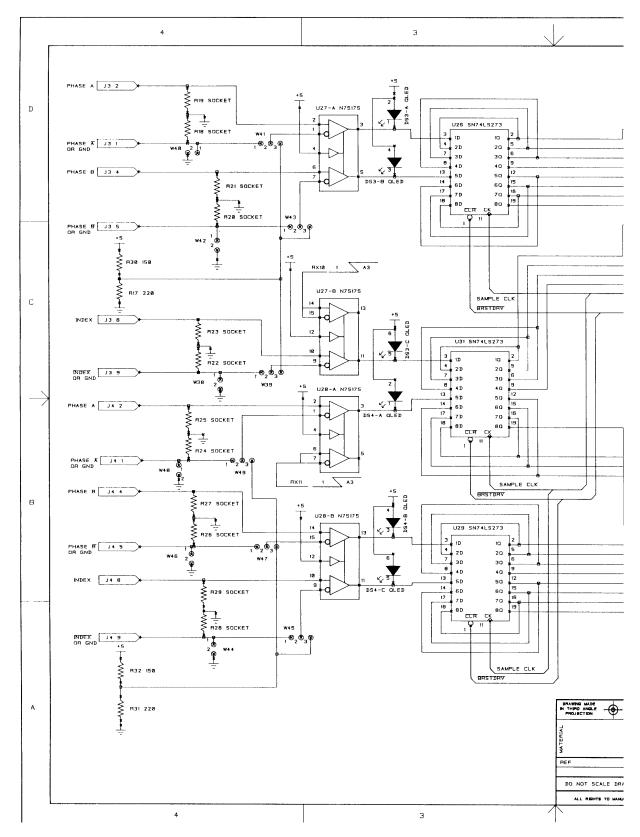

| Figure D.1 5312B Schematic Sheet 1 of 5, Left Half of sheet                  |

| Figure D.2 5312B Schematic Sheet 1 of 5, Right Half of sheet                 |

| Figure D.3 5312B Schematic Sheet 2 of 5, Left Half of sheet                  |

| Figure D.4 5312B Schematic Sheet 2 of 5, Right Half of sheet                 |

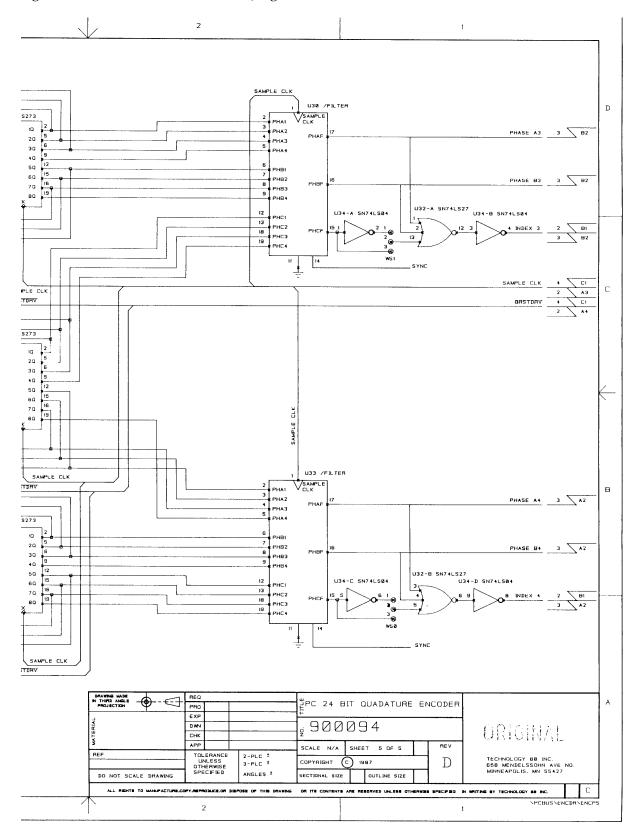

| Figure D.5 5312B Schematic Sheet 3 of 5, Left Half of sheet                  |

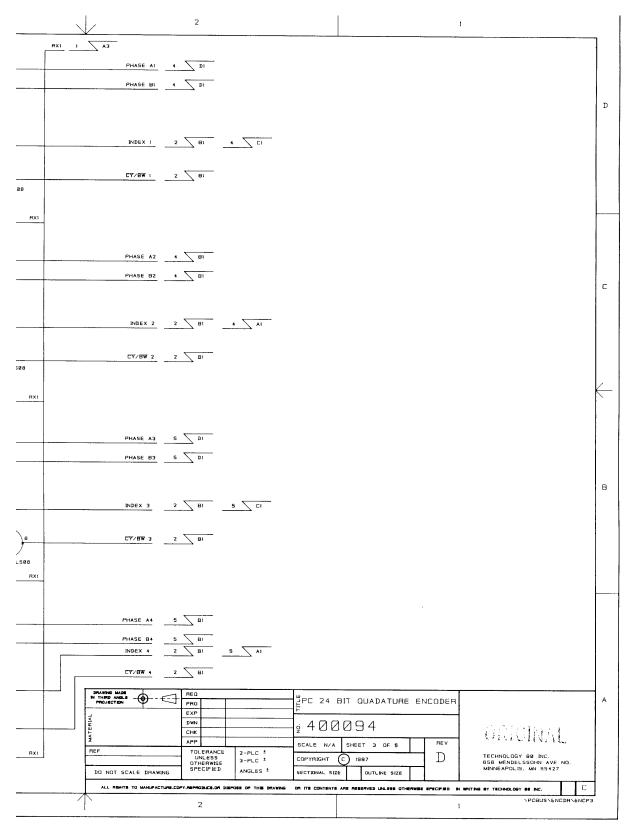

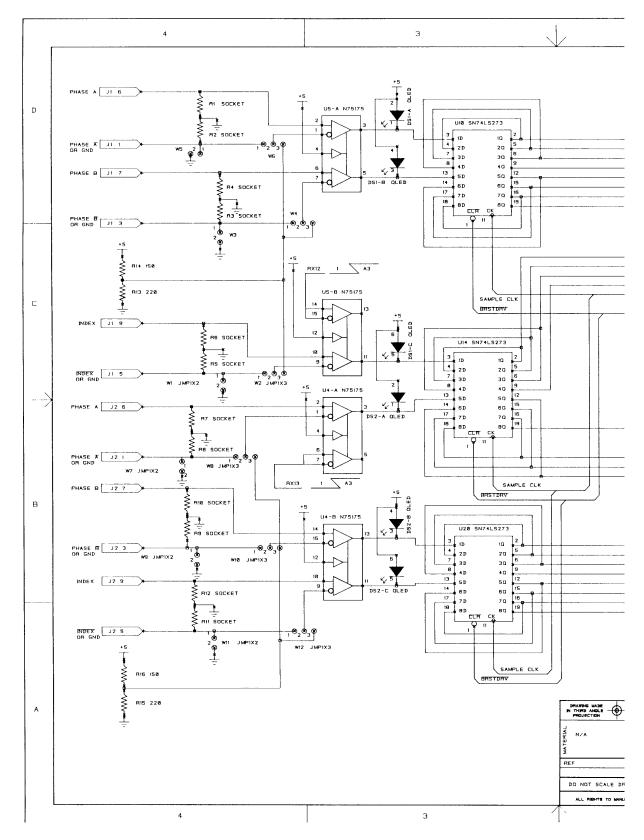

| Figure D.6 5312B Schematic Sheet 3 of 5, Right Half of sheet75               |

| Figure D.7 5312B Schematic Sheet 4 of 5, Left Half of sheet                  |

| Figure D.8 5312B Schematic Sheet 4 of 5, Right Half of sheet                 |

| Figure D.9 5312B Schematic Sheet 5 of 5, Left Half of sheet                  |

| Figure D.10 5312B Schematic Sheet 5 of 5, Right Half of sheet                |

# About this Manual Set

### **Quality Control**

ACS-Tech80 manufactures quality and versatile products, and we want our documentation to reflect that same quality. We take great pains to publish manuals that are informative and well organized. We also strive to make our documentation easy to understand for the novice as well as the expert.

If you have comments or suggestions about how to make this (or other) manuals easier to understand or if you find an error or an omission, please email us at <u>support@acs-tech80.com</u>. You will receive a complimentary updated manual.

### Conventions

#### Procedural

ACS-Tech80 uses various conventions throughout this and all other manuals. You should become familiar with these conventions as they are used to draw attention to items of importance and items that will generally assist you in understanding a particular area.

When referring to pin numbering, pin 1 is *always* associated with a square solder pad on the actual component footprint.

#### Notational

A forward slash (/) preceding a signal name denotes an active LOW signal. This is a standard Intel convention.

*Caret* brackets (<>) denote keystrokes. For instance <Enter> represents carriage—return— with—line—feed keystroke, and <Esc> represents an escape keystroke.

Driver routine declarations are shown for C and BASIC (where applicable).

*Hungarian* notation is used for software parameters. In other words, the parameter type is denoted by a one or two letter small case prefix:

| с  | character, signed or unsigned. |

|----|--------------------------------|

| S  | short integer, signed          |

| W  | short integer, unsigned        |

| 1  | long integer, signed           |

| dw | long integer, unsigned         |

For example, *wBoardAddr* would be an unsigned short integer parameter.

An additional p prefix before the type prefix indicates that the parameter is being passed by reference instead of by value. (A pointer to the variable is being passed instead of the variable itself.)

For example, *pwErr* would be an unsigned short integer parameter passed by reference.

This notation is also used in BASIC although no distinction between signed and unsigned variables exists.

In BASIC, all parameters also have a type suffix:

| \$ | character, signed or unsigned    |

|----|----------------------------------|

| %  | integer, signed or unsigned      |

| &  | long integer, signed or unsigned |

Routine names are printed in bold plain font when they appear outside of function declarations, e.g., ReadStatus.

Parameter names are printed in italics when they appear outside of function declarations, e.g. *sControls*.

Constants are defined with all caps, e.g., ALL\_AXES. Underscores (\_) must be replaced by periods (.) for use with BASIC.

Combinational logic and hexadecimal notation is in C convention in many cases. For example, the hexadecimal number 7Ch is shown as 0x7C.

C relational operators for OR and AND functions—"| |" and "&&"—are used to minimize the confusion associated with grammar.

This type of box is used to indicate important information needed to perform an action or information that is *nice-to-know*.

### How This Book Is Organized

#### **Front Section**

A TOC (Table of Contents) lists all the sections, appendices, and attachments in the manual set. In addition, the TOC lists all figures, tables, and sample code where applicable.

#### Section 1 Introduction and Installation

This section offers a general overview of the 5312B and provides the information you will need to get the 5312B and running.

#### Section 2 Operation and Programming

This section gives a detailed discussion on the 5312B and a theory of operation for the encoder chipset. It also covers talking to the 5312B and programming the chipset and registers at a low level.

#### Section 3 Interrupt control

This section discusses how to program the onboard 8259A Programmable Interrupt Controller (PIC).

#### Appendix A PC I/O and Interrupt Mapping

This appendix breaks down PC I/O and interrupt space by address and function.

#### Appendix B Tech Bulletins and Application Notes

This appendix offers pertinent bulletins and notes to assist in your application development.

#### Appendix C Revision History

This appendix keeps a running log of all top level assembly revision changes during the life of the board.

#### Appendix D Circuit Diagrams

Circuit diagrams for the 5312B.

# **Before Installing the Model 5312B**

### **Unpacking and Inspection**

Each model 5312B card is carefully sealed in a static protected bag, surrounded by bubble wrap, packed in anti—static Styrofoam peanuts or some other shock absorbing medium, and shipped in a sturdy cardboard carton. We quality check each shipment for integrity and content.

Inspect the shipping carton for any signs of damage. If you find visible damage, contact Tech 80 immediately.

Check the contents, and verify the contents with the packing list attached to the outside of the shipping carton. If you find any discrepancies, contact ACS-Tech80 immediately.

## **Electrostatic Discharge (ESD)**

ESD damage is the leading cause of (electrical) infant mortality failures in electronic equipment using integrated circuits. The most susceptible technologies include MOS and high speed DSP processors, due to their submicron internal construction. The 5312B contains ESD sensitive components.

The basics of electrostatic buildup are simple. An electrostatic charge is built up between two devices much like the charge built between two plates of a capacitor. One body is charged to some potential like one plate of a capacitor (5312B card); another body is charged to another potential (perhaps your body or the chassis of the PC). In the middle, an insulator gap (a dielectric such as air) prevents the two sides from equalizing the charge. In the event the two sides come in physical contact, they will violently equalize in the form of an electric spark between them.

A static potential of many thousands of volts can be generated by walking over some distance from your workbench to the computer chassis simply due to physics principle of conservation of charge. Whatever you touch is also at the same potential. If the board you hold is the first thing to come in contact with the PC chassis (or some other medium), the board will equalize to the other potential through the paths of least resistance—by punching through p/n junctions and submicron insulation layers between conductive and semiconductive paths in the integrated circuits.

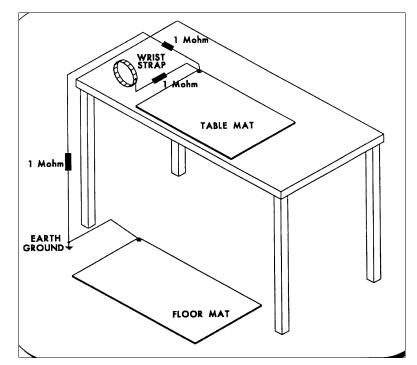

Adhering to the following simple 3M® guidelines easily prevents damage due to ESD:

• Handle all static-sensitive components at a **Static Safeguarded** work area (see figure 1.1 for an example).

A **Static Safe** area is any area that is capable of controlling static charge on conductive materials, people, and non-conductive materials.

• Transport and store all static—sensitive components in **Static Shielding** containers or packages.

A **Static Shield** must be capable of protecting from static discharge as well as static fields.

Manufacturers such as 3M<sup>®<sup>1</sup></sup> offer a complete line of UL® approved grounding systems. Table 1 lists an assortment of 3M<sup>®</sup> products and part numbers.

| Table 1.0 3M® Grounding System Components.                             |                  |

|------------------------------------------------------------------------|------------------|

| The following items comprise a typical                                 | workstation.     |

| Component                                                              | Part Number      |

| Table Mat 2x4 feet                                                     | 8020             |

| Floor Mat 4x5 feet                                                     | 8200             |

| Grounding Cord                                                         | 3040             |

| Wrist Strap/Table Mat Grounding System                                 | 3048             |

| Adjustable Wrist Strap                                                 | 2214             |

| Note: Call 800-328-1368 for ordering inform complete list of products. | nation and for a |

<sup>1</sup>3M<sup>®</sup> is a registered trademark of Minnesota Mining and Manufacturing.

Figure 1 A typical ESD workstation.

The resistors are necessary to safely limit the current in the event that you should cross a live electrical source.

# **Development Kit**

Accessories included in the development kit enable you to get your application up and running with a minimum of difficulty. The following is a brief summary of the contents. In addition to the manual set, you get...

#### • Driver/Demo Software

Drivers written in C, Pascal, and BASIC to streamline program writing, and a profile utility program to set up register values for given profile parameters.

#### • Designing With Motion Handbook (9009)

A definitive reference book on motion control.

#### • Cable (CAB5312-4-36)

A cable to connect 3 axes to terminal board TB5ON-S.

#### • Terminal Board (TB50N-S)

A terminal board that connects the 5312B to the outside world through convenient screw-on terminals.

## **Basic Tools and Test Equipment**

To properly develop, check out, and troubleshoot this system, as with any system, you must have the proper tools and equipment.

The first tools you will use are the *Model 5312B Hardware Guide* (this document) and the *Model 5312B Software Guide*. Read the manuals thoroughly, and you will find answers to the bulk of your questions before you have to call Technical Support.

In addition to the manuals, you should have some basic tools and equipment at your disposal. They include:

#### Calculator

A *Texas Instrument TI-35* or equivalent calculator that will convert decimal and hexadecimal back and forth and perform unit conversion, is a must.

#### • Basic Hand Tools

Have available, a complete set of common hand tools commensurate with your application. Vendors such as *Jensen* or *Techni—Tool* offer a wide range of complete tool kits to cover virtually every need.

#### • Oscilloscope

A good quality 10 MHz. oscilloscope is invaluable for real-time system tuning and troubleshooting. *Tektronix* and *Hewlett Packard* offer a wide choice to cover every application and price range.

#### • Multimeter

A *Fluke 25* or equivalent digital multimeter is relatively inexpensive and will become one of the most used tools in your tool box.

#### • Logic Probe

Any logic probe on the market, 1 MHz. or faster, is adequate. A logic probe is extremely useful for troubleshooting system interrupt, encoder, limit, and I/O problems, and it is inexpensive.

#### • Model 9011 Motion Simulator

The 9011, manufactured by Tech 80, offers a convenient and safe way to test system software without the need to connect to real hardware. See appendix G.

To supplement the above list, test equipment for testing and troubleshooting might include:

#### • Tach Generator

Often times you will need to know the velocity in real time of an axis for the purpose of tuning or troubleshooting. A *StroboTac* or a portable tach generator that you can fix on to the shaft of an axis is a useful tool.

#### • Frequency Counter

For accurate measurement of encoder counts or counting other pulse trains, a frequency counter is very useful.

Intentionally Left Blank

# 1 Introduction and Installation

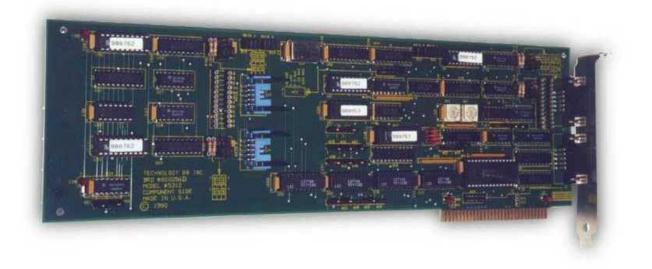

## **1.1 Description**

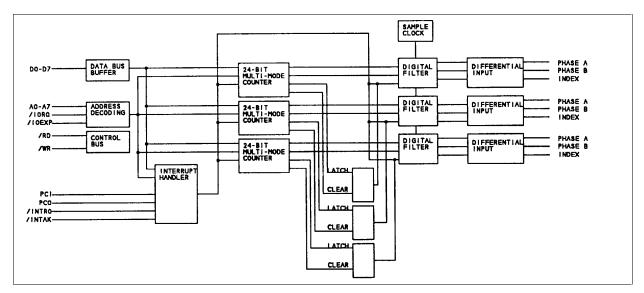

The 5312B Quadrature Encoder card is PC Bus compatible. It provides inputs and decoding for up to four incremental quadrature encoders depending on the model purchased. You may also use the card as a high-speed pulse counter (up/down and pulse/direction) for general counting applications. Figure 1.1 on the next page shows a functional block diagram.

NOTE This manual is model independent. For models not using all encoder ports, disregard the appropriate upper axes.

Figure 1.1 Functional block diagram for the 5312B

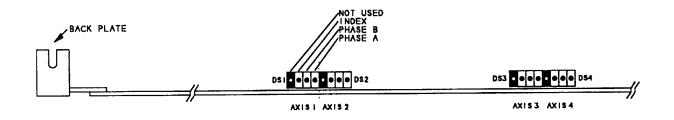

For each encoder circuit, Phase A (Phase 0), Phase B (Phase 90), and Index pulse inputs are provided. Jumper options on board allow you to configure the inputs as single-ended TTL or differential (the recommended connection method). Individual connectors for each encoder provide power (+5V) and ground for the encoder if needed.

You can also use the 5312B as pulse counter for up to 4 independent events, or you can cascade the counters to provide high-speed pulse counting over an extended count range.

A 4-stage digital filter conditions inputs. The filter clock is one of five jumper-selectable sampling frequencies ranging up to 10 MHz. Selecting the lowest frequency compatible with the highest expected input rate will maximize noise immunity. The maximum input rate per phase in quadrature decode mode is approximately 333 kHz. The maximum input rate in count mode is approximately 1.25 MHz. Sample clock frequency selection is described in detail in section 2.

The conditioned inputs are applied to a 24-bit counter provided for each encoder. You can use the counters for quadrature decoding, pulse and direction input counting, or as a pulse input up/down counter. Count output is available for the PC Bus in binary or binary coded decimal (BCD) form. The count value may be latched on command, latched on an index pulse, or latched with a new count value when an index pulse occurs.

The 5312B is capable of generating interrupts. Maskable interrupts may come from a valid index pulse, counter overflow / underflow, or on count value match with a preset compare value.

| Voltage Requirements : | 4- axis:1.5A(typical), 2.0 A (maximum)  |

|------------------------|-----------------------------------------|

|                        | 3- axis:1.25A(typical), 1.75A (maximum  |

|                        | 2- axis: 1.0A(typical), 1.5A (maximum)  |

|                        | 1- axis: 0.9A(typical), 1.25A (maximum) |

| Compatibility:         | PC/XT/AT                                |

|                        | Single-ended or Differential            |

|                        | Incremental Encoders                    |

|                        | 1 to 12 VDC TO GROUND                   |

|                        | TTL or CMOS Signal Sources              |

| Operating Range        | 0 to 70 degrees Celsius                 |

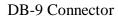

| Mating Connectors      | 9-pin Dsub Ansley 609-9p                |

| 0                      | Amphenol                                |

|                        | 841-17-DEFR-B09P                        |

| Card Dimensions        | 13.3x4.2x0.5 inches                     |

# **1.2 Technical Specifications**

### **1.3 Setting the Jumpers**

**CAUTION** Always remove power from the PC and any external system devices before removing any connection on the 5312. Failure to do so may result in permanent damage to the card and WILL void any warranty.

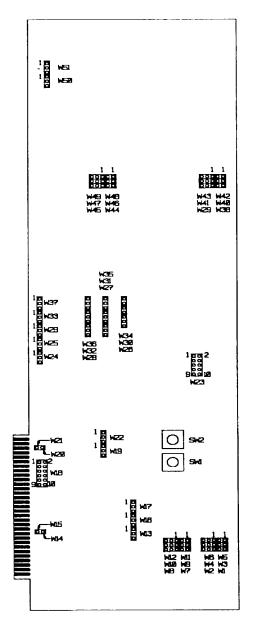

Jumper options on the 5312B offer a great deal of flexibility in system operation. These options are grouped into 4 areas according to functions—encoder inputs, card functions, interrupt action, and card addressing.

All cards are shipped with most jumpers installed for a given configuration. All factory default jumpers are indicated throughout this manual in the appropriate tables with a "†" symbol. However, due to possible rough handling during shipment, there is no assurance that all jumpers will be in the indicated position.

| NOTE | Default jumper settings shown are those       |

|------|-----------------------------------------------|

|      | for the 4-axis version of the M5312. For      |

|      | default settings on other versions, see table |

|      | 1.13 at the end of the section 1.             |

| 1    |                                               |

#### Check and properly configure all boards before installing.

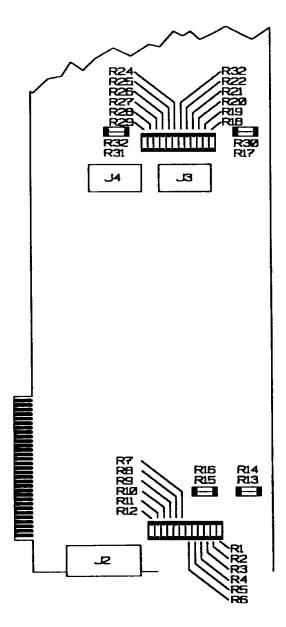

Jumper locations are shown in figure 1.2. We strongly recommend, however, once you determine the proper jumper settings, that you replace all jumpers with more reliable wire-wrapped connections. This is particularly important when exposing the card to an industrial environment where vibration, dust, oil, or other contaminants may be present.

#### 1.3.1 Base Addressing

Jumper W19 determines the upper nibble (4 bits) of the card base address according to Table 1.1.

| Table 1.1 W19, Base Address Select (upper nibble) |              |

|---------------------------------------------------|--------------|

| W19                                               | Base Address |

| (1-2) †                                           | 2xxh         |

| (2-3)                                             | 3xdi         |

† Default jumper setting.

Set hex switches SW1 and 5W2 to determine the lower 8 bits of the address. Switch 5W2 represents the most significant nibble (MSN), and SW1 represents the least significant nibble (LSN). Since the 5312B occupies two adjacent I/O ports, only the even settings of the LSN switch are used.

Figure 1.2 Jumper locations for the 5312B.

#### **1.3.2 Indirect Addressing**

To conserve I/O space on the PC Bus, the 5312B is indirectly addressed (see table 1.2). This allows the card to occupy only two direct I/O ports by using one for indirect addressing (even or lower) and the other for data (the odd or greater of the two ports). The sequence for writing to any indirect port is to first write the indirect port address to the address port. The desired data can then be written to the data port. This indirect port will remain addressed until the indirect address port is again written. For example, to write the initialization bytes MCR, ICR, OCCR, and QR to the command port of axis 1 assuming the card is strapped to 300h as the base address:

- 1.) Write the indirect address for the axis A command port (01h) to the indirect address port (300h).

- 2.) Write the first byte (Master Control Register) to the data port (301h).

- 3.) Write the second byte (Input Control Register) to the data port (301h).

- 4.) Write the third byte (Output/Counter Control Register) to the data port (301h).

- 5). Write the last byte (Quadrature Encoder) to the data port (301h).

| NOTE | The C function libraries on the software diskette make this sequence |

|------|----------------------------------------------------------------------|

|      | transparent to the user.                                             |

| Axis   | Address | When Written                                                                | When Deed                                                                         |

|--------|---------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 1      | 00      | Write to preset register (PR) and<br>increment register address<br>counter. | When Read<br>Read OL (output latch) and<br>increment register address<br>counter. |

|        | 01      | Write to command register.                                                  | Read OSR (output status register).                                                |

| 2      | 02      | Write to PR and increment register address counter.                         | Read OL and increment register address counter.                                   |

|        | 03      | Write to command register.                                                  | Read OSR.                                                                         |

| 3      | 04      | Write to PR and increment register address counter.                         | Read OL and increment register address counter.                                   |

|        | 05      | Write to command register.                                                  | Read OSR.                                                                         |

| 4      | 06      | Write to PR and increment register address counter.                         | Read OL and increment register address counter.                                   |

|        | 07      | Write to command register.                                                  | Read OSR.                                                                         |

| Global | 08      | Global write to all four PRs.                                               | Invalid                                                                           |

|        | 09      | Global write to all four command registers.                                 | Invalid                                                                           |

| PlC    | 0A      | Low Port                                                                    | Low Port                                                                          |

|        | 0B      | High Port                                                                   | High Port                                                                         |

#### **1.3.3 Termination Resistors**

If differential input is used, give consideration to terminating the cable lines connecting the signal to the card. Cable length and signal frequency determines how critical the termination factor is. Since the needed termination resistor value is determined by cable type, sockets are provided for easy insertion and removal of termination resistors. Unless otherwise specified by the encoder manufacturer, one-quarter watt carbon film resistors of a standard EIA value closest to one half the characteristic impedance of the cable are adequate (see cable manufacturers specification for values). Termination resistors apply a load to the signal source, so make sure that the source can supply enough drive capability to compensate for this condition.

Figure 1.3 shows the termination resistor locations for both single-ended and differential. Table 1.3 shows the termination resistor assignments for each signal in differential mode. The inputs should be terminated in the characteristic impedance of the input line.

| Table 1.3 Termination Resistors in Differential Mode       |        |         |          |          |  |  |  |

|------------------------------------------------------------|--------|---------|----------|----------|--|--|--|

| Signal                                                     | Axis 1 | Axis 2  | Axis 3   | Axis 4   |  |  |  |

| Phase A                                                    | R1, R2 | R7, R8  | R18, R19 | R24, R25 |  |  |  |

| Phase B                                                    | R3, R4 | R9, R10 | R20, R21 | R26, R27 |  |  |  |

| Index $R5, R6$ $R11, R12$ $R20, R21$ $R20, R27$ $R28, R29$ |        |         |          |          |  |  |  |

When single-ended encoder inputs are used, the logic level of the input signal is determined by comparison with a reference voltage on the card. A pair of resistors selected and inserted by the user sets this reference, and they form a voltage divider network that establishes the center point for the input Hysteresis band.

Resistor assignments in a single-ended mode are shown in table 1.4

| Table 1.4 Termination Resistors in Single-Ended Mode |        |        |        |        |  |  |

|------------------------------------------------------|--------|--------|--------|--------|--|--|

| Typical Value                                        | Axis 1 | Axis 2 | Axis 3 | Axis 4 |  |  |

| 220 Ohms                                             | R14    | R15    | R17    | R31    |  |  |

| 150 Ohms R14 R16 R30 R32                             |        |        |        |        |  |  |

The 5312B features encoder input indicators that are useful when determining proper encoder operation and connection. Only three of the four LEDs in each package are used. Figure 1.4 shows the location of LEDs on the outboard edge of the card as you view down from the top. An LED is on when its corresponding input signal is LOW.

Figure 1.3 Encoder termination resistor locations

Figure 1.4 LED locations on the card edge.

#### 1.3.4 Selecting an Index Option

The following are the available jumper options that direct the function of the encoder index pulse. The first two options work in conjunction with bits D4 and D5 respectively of the Input Control Register (ICR). Table 1.5 shows the jumper configuration for selecting an index option.

Index Action to /ABGT (ABGate) or /RCTR (Reset Counter):

ICR B4 = 0: A valid index level will reset the counter.

ICR B4 = 1: A valid index level will gate phase A and B inputs to the counter.

Index Action to /LCTR (Load Counter) or /LLTC (Load output Latch).

ICR BS = 0: A valid index level will load the contents of the preset register into the counter.

ICR B5 = 1: A valid index level will load the contents of the counter into the Output Latch.

Active Low Index Polarity.

Select this option if the encoder provides an active LOW index pulse.

Active High Index Polarity.

Select this option if the encoder provides an active HIGH index pulse.

Correct strapping for each axis is detailed in table 1.6 below. The following tables also provide the necessary jumpering information for operating the encoder.

**NOTE** If Index is not used, remove jumpers W17, W22, and W29. Failure to do so will result in incorrect encoder operation. If Index is used, We recommend that you check for correct encoder operation with the jumpers removed, then with the jumpers installed.

| Table 1.5 Index Option Selections. |            |             |            |           |  |  |

|------------------------------------|------------|-------------|------------|-----------|--|--|

| Operation                          | Axis 1     | Axis 2      | Axis 3     | Axis 4    |  |  |

| Index Action<br>/ABGT-/RCTR†       | W24(2-3)   | W17(2-3)    | W22(2-3)   | W29(2-3)  |  |  |

| (AB Gate-Reset Counter)            |            |             |            |           |  |  |

| Index Action<br>/LCTR-/LLTC†       | W24(1 -2)† | W1 7(1 -2)† | W22(1 -2)† | W29(1-2)† |  |  |

| (Load Counter-Load Latch)          |            |             |            |           |  |  |

| Active LOW Index Polarity          | W13(2-3)†  | W16(2-3)‡   | W51(2-3)†  | W50(2-3)† |  |  |

| Active HIGH Index Polarity         | W1 3(1-2)  | W16(1-2)†‡  | W51(1-2)   | W50(1-2)  |  |  |

NOTE: A forward slash preceding a signal name denotes an active LOW signal.

† Default jumper setting.

‡ For axis 2, strap (1-2) for active LOW, (2-3) for active HIGH

| Axis | Operating Mode | Jumpers       | Strapping |

|------|----------------|---------------|-----------|

| 1    | Differential   | W1, W3, W5    | none      |

|      |                | W2,W4,W6      | (1-2)     |

|      | Single-Ended   | W1,W3, W5     | (1-2)†    |

|      |                | W2, W4, W6    | (2-3)†    |

| 2    | Differential   | W7, W9, W1 1  | none      |

|      |                | W8, W10, W12  | (1-2)     |

|      | Single-Ended   | W7, W9, W1    | (1-2)†    |

|      |                | W8, W10, W12  | (2-3)†    |

| 3    | Differential   | W38, W40, W42 | none      |

|      |                | W39, W41, W43 | (1-2)     |

|      | Single-Ended   | W38, W40, W42 | (1-2)†    |

|      |                | W39, W41, W43 | (2-3)†    |

| 4    | Differential   | W44, W46, W48 | none      |

|      |                | W45, W47, W49 | (1-2)     |

|      | Single-Ended   | W44, W46, W48 | (1-2)†    |

|      |                | W45, W47, W49 | (2-3)†    |

† Default jumper setting.

#### **1.3.5 Selecting the Card Configuration**

The following tables provide the necessary jumpering information for selecting card function.

#### **Sample Clock Frequency Jumpering**

Jumper W23 (table 1.7) is used to select the sample clock frequency used by the digital filters. For more information, see section 2.

| Table 1.7 Sample Clock Frequency Jumper Settings |  |  |  |  |

|--------------------------------------------------|--|--|--|--|

| W23                                              |  |  |  |  |

| (9-10)†                                          |  |  |  |  |

| (7-8)                                            |  |  |  |  |

| (5-6)                                            |  |  |  |  |

| (3-4)                                            |  |  |  |  |

| (1-2)                                            |  |  |  |  |

|                                                  |  |  |  |  |

† Default jumper setting.

#### **Counter Cascading**

If you need to extend the counting range of the 5312B, you can cascade the counters according to table 1.8.

| Table 1.8 Cascading the Counters |          |           |  |  |  |

|----------------------------------|----------|-----------|--|--|--|

| Operation                        | Jumper   | Strapping |  |  |  |

| Cascade Axis 1 to Axis 2         | W28, W25 | (2-3)     |  |  |  |

| No Cascading Axis 1 to Axis 2    | W28, W25 | (1 -2)†   |  |  |  |

| Cascade Axis 2 to Axis 3         | W27, W31 | (2-3)     |  |  |  |

| No Cascading Axis 2 to Axis 3    | W27, W31 | (1-2)†    |  |  |  |

| Cascade Axis 3 to Axis 4         | W33, W37 | (2-3)     |  |  |  |

| No Cascading Axis 3 to Axis 4    | W33, W37 | (1-2)†    |  |  |  |

† Default jumper setting.

#### **1.3.6 Interrupt Selection** <u>Enabling and Disabling PIC Interrupts</u>

Table 1.9 provides the necessary information for enabling and disabling Programmable Interrupt Control (PIC) interrupts. For further information on interrupt selection, refer to section 2.

| Table 1.9 Jumpering for Disabling/Enabling Borrow Interrupts        |        |        |        |        |           |

|---------------------------------------------------------------------|--------|--------|--------|--------|-----------|

| Operation                                                           | Axis 1 | Axis 2 | Axis 3 | Axis 4 | Strapping |

| Disable <sup>‡</sup> /BW <sup>†</sup> (borrow)<br>output to the PlC | W26    | W32    | W35    | W36    | (1-2)     |

| Enable /BW† output to the PlC                                       | W26    | W32    | W35    | W36    | (2-3)†    |

A forward slash (/) preceding a signal name denotes an active LOW signal

† Default jumper setting.

‡ Disable /BW to use comparator mode

#### PC Bus Interrupts

W18 selects the PC Bus interrupt request line used for interrupt operation as shown in table 1.10.

| Table 1.10 Selecting an Interrupt |              |                       |           |  |  |  |

|-----------------------------------|--------------|-----------------------|-----------|--|--|--|

| W18                               | Interrupt    | Hardware Interrupt    | Interrupt |  |  |  |

|                                   | Request Line |                       | Number    |  |  |  |

| (1-2)                             | IRQ2         | Unused‡               | 0Ah       |  |  |  |

| (3-4)†                            | IRQ3         | Unused                | 0Bh       |  |  |  |

| (5-6)                             | IRQ4         | Serial Port           | 0Ch       |  |  |  |

| (7-8)                             | IRQ5         | Unused                | 0Dh       |  |  |  |

| (9-10)                            | IRQ6         | Diskette Port         | 0Eh       |  |  |  |

| (11-12)                           | IRQ7         | Parallel Printer Port | 0Fh       |  |  |  |

† = Default jumper setting.

‡ = Unused on XT only, not available on AT

#### 1.3.7 Wait States

A wait state is a period of time requested by a peripheral device to pause the host computer during a read or write operation. A device pauses the host to ensure that valid data are passed. Each wait state is equal to 1 clock cycle. Without wait states on the host, faster PCs will terminate an operation before the peripheral card can fully and reliably gate the data in from or out to the PC bus. As shipped, the card is jumpered for 2 wait states, although some slower PCs may be able to use the card with less than 2. Jumpers W34 and W30 determine the number of wait states as shown in table 1.11.

| Table 1.11 Generating Wait States |           |           |  |  |  |  |

|-----------------------------------|-----------|-----------|--|--|--|--|

| Wait State                        | W34       | W30       |  |  |  |  |

| None                              | none      | none      |  |  |  |  |

| 1                                 | none      | installed |  |  |  |  |

| 2 installed None †                |           |           |  |  |  |  |

| Invalid                           | Installed | Installed |  |  |  |  |

† Default jumper setting.

### **1.4 Installation**

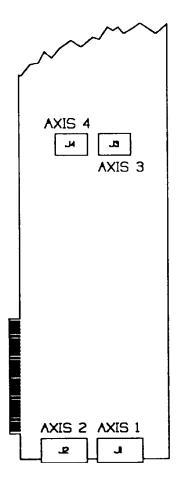

The 5312B is designed to operate in a PC backplane or on a motherboard. You may install the board into any 8-bit slot in the PC according to the PC manufacturer's instructions. If you use more than 2 of the 4 available axes, an additional expansion slot is required. Connect ribbon cables as required from J3 and J4 to the additional back plate.

Give consideration to power and ground connections to ensure reliable system operation. Encoder connections are made to the card through up to 4 9-pin, Dsub connectors. Board connections are located according to figure 1.5.

The pin assignments for these connectors are shown in section 1.4.2.

#### Properly phase the encoder according to manufacturer's instructions.

Figure 1.5 Connector locations on the board

#### **1.4.1 Power Considerations**

The Model 5312B requires +5V from the PC Bus. The typical current load is 1A with a maximum of 1.5A depending on the number of axes used. In addition, +5V is available at J1, J2, J3, and J4 for any external devices that need +5V. The total current load must be considered when determining how much power is required for the system.

#### **1.4.2 Connector Pinouts**

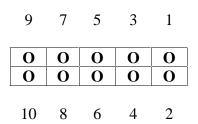

Table 1.12 lists the pin assignments for J1 to J4. The view shown of the connector is looking into the board from the backpanel. Figure 1.5 shows the connector locations on the board. Ribbon cables connect axes 3 and 4 from the 10—pin unshrouded headers to chassis I/O slots on the backpanel. The pinout on the backpanel connectors is the same as for axes 1 and 2.

**Ribbon Cable Connector**

| Table 1.12 Connector J1-J4 Pin Assignments. |     |              |              |  |  |  |

|---------------------------------------------|-----|--------------|--------------|--|--|--|

| Ribbon                                      | Pin | Single-Ended | Differential |  |  |  |

| 1                                           | 1   | Ground       | /Phase A +   |  |  |  |

| 3                                           | 2   | +5V          | +5V          |  |  |  |

| 5                                           | 3   | Ground       | /Phase B†    |  |  |  |

| 7                                           | 4   | +5V          | +5V          |  |  |  |

| 9                                           | 5   | Ground       | /Index †     |  |  |  |

| 2                                           | 6   | Phase A      | Phase A      |  |  |  |

| 4                                           | 7   | Phase B      | Phase B      |  |  |  |

| 6                                           | 8   | Ground       | Ground       |  |  |  |

| 8                                           | 9   | Index        | Index        |  |  |  |

<sup>†</sup> A forward slash (/) preceding a signal name denotes an active LOW signal.

| Table 1.13 Default Jumper settings For All Board Versions. |        |        |        |        |  |

|------------------------------------------------------------|--------|--------|--------|--------|--|

| Jumper                                                     | 4-Axis | 3-Axis | 2-Axis | 1-Axis |  |

| W1                                                         | (1-2)  | (1-2)  | (1-2)  | (1-2)  |  |

| W2                                                         | (2-3)  | (2-3)  | (2-3)  | (2-3)  |  |

| W3                                                         | (1-2)  | (1-2)  | (1-2)  | (1-2)  |  |

| W4                                                         | (2-3)  | (2-3)  | (2-3)  | (2-3)  |  |

| W5                                                         | (1-2)  | (1-2)  | (1-2)  | (1-2)  |  |

| W6                                                         | (2-3)  | (2-3)  | (2-3)  | (2-3)  |  |

| W7                                                         | (1-2)  | (1-2)  | (1-2)  | none   |  |

| W8                                                         | (2-3)  | (2-3)  | (2-3)  | none   |  |

| W9                                                         | (1-2)  | (1-2)  | (1-2)  | none   |  |

| W10                                                        | (2-3)  | (2-3)  | (2-3)  | none   |  |

| W11                                                        | (1-2)  | (1-2)  | (1-2)  | none   |  |

| W12                                                        | (2-3)  | (2-3)  | (2-3)  | none   |  |

| W13                                                        | (2-3)  | (2-3)  | (2-3)  | (2-3)  |  |

| W16                                                        | (1-2)  | (1-2)  | (1-2)  | none   |  |

| W17                                                        | (1-2)  | (1-2)  | (1-2)  | none   |  |

| W18                                                        | (3-4)  | (3-4)  | (3-4)  | (3-4)  |  |

| W19                                                        | (1-2)  | (1-2)  | (1-2)  | (1-2)  |  |

| W22                                                        | (1-2)  | (1-2)  | none   | none   |  |

| W23                                                        | (9-10) | (9-10) | (9-10) | (9-10) |  |

| W24                                                        | (1-2)  | (1-2)  | (1-2)  | (1-2)  |  |

| W25                                                        | (1-2)  | (1-2)  | (1-2)  | none   |  |

| W26                                                        | (2-3)  | (2-3)  | (2-3)  | (2-3)  |  |

| W27                                                        | (1-2)  | (1-2)  | none   | none   |  |

| W28                                                        | (1-2)  | (1-2)  | (1-2)  | none   |  |

| Table 1.13 [ | Default Jumper se | ettings For All B | oard Versions | (Continued.) |

|--------------|-------------------|-------------------|---------------|--------------|

| Jumper       | 4-Axis            | 3-Axis            | 2-Axis        | 1-Axis       |

| W29          | (1-2)             | none              | none          | none         |

| W30          | none              | none              | none          | none         |

| W31          | (1-2)             | (1-2)             | none          | none         |

| W32          | (2-3)             | (2-3)             | (2-3)         | none         |

| W33          | (1-2)             | none              | none          | none         |

| W34          | (1-2)             | (1-2)             | (1-2)         | (1-2)        |

| W35          | (2-3)             | (2-3)             | none          | none         |

| W36          | (2-3)             | none              | none          | none         |

| W37          | (1-2)             | none              | none          | none         |

| W38          | (1-2)             | (1-2)             | none          | none         |

| W39          | (2-3)             | (2-3)             | none          | none         |

| W40          | (1-2)             | (1-2)             | none          | none         |

| W41          | (2-3)             | (2-3)             | none          | none         |

| W42          | (1-2)             | (1-2)             | none          | none         |

| W43          | (2-3)             | (2-3)             | none          | none         |

| W44          | (1-2)             | none              | none          | none         |

| W45          | (2-3)             | none              | none          | none         |

| W46          | (1-2)             | none              | none          | none         |

| W47          | (2-3)             | none              | none          | none         |

| W48          | (1-2)             | none              | none          | none         |

| W49          | (2-3)             | none              | none          | none         |

| W50          | (2-3)             | none              | none          | none         |

| W51          | (2-3)             | (2-3)             | none          | none         |

# **2** Operation and Programming

## 2.1 Theory of Operation

The Model 5312B can be configured for up to 4 independent 24-bit multimode counters depending on the model purchased. All models are PC/XT/AT compatible. For applications requiring more than 24 bits of count range, the counters can be cascaded together to form various 24-bit counter configurations. For example, you can cascade counters to obtain one 48-bit counter, a 24-bit counter and a 72-bit counter, or even one 96-bit counter.

Each counter is capable of numerous modes. Examples include:

- A/B quadrature with a maximum input frequency of .333 MHz,

- Up/down count with a maximum input frequency of 1.25 MHz,

- Count/direction with a maximum input frequency of 1.25 MHz,

- Divide by *n* mode with a maximum input frequency of 1.25 MHz.

All three inputs to each counter—Phase A, Phase B, and Index—can be connected single-ended TTL or differential for greater noise immunity. The 5312B provides sockets in differential mode to allow you to easily insert termination resistors. The input lines do not need to be terminated, but for best noise immunity terminate them at the characteristic impedance of the input line. Each input is tied through a buffer to an LED which is turned on when the respective input is LOW.

Each input is digitally filtered (see section 2.2.10) using a sample clock rate that can be optimized for your signal input rate. The index input can be used to generate an interrupt or any one of the following:

- Resetting the counter

- Enabling the gate for phase A and B inputs

- Transferring the 24-bit count value to the count latch

The counter can generate an interrupt on an overflow /underflow or on a compare match condition between the counter and the preset register.

An 8259 Programmable Interrupt Controller (PIC) handles interrupts, and the PIC can be polled to determine the cause of the interrupt.

Multiple 8-bit reads and writes handle the PC Bus interface to each counter. The 24-bit value is read or written, LSB first (little endian).

# 2.2 Programming

Programming the 5312B requires that you read and write the board multimode counter. By understanding the functions of all registers and knowing how to access them, you will be able to issue commands to the board. The following is a discussion of each register.

### 2.2.1 Writing the Preset Register (PR)

To load the PR:

1.) Reset the PR and the Output Latch address counter by writing 01h to the Command Register (see below).

2.) Write the three bytes that will comprise the 24-bit value of the PR by writing the LSB first and the MSB last.

## 2.2.2 Reading the Output Latch Register (OL)

To read the OL:

- 1.) Reset the PR and OL address counter by writing 01h to the Command Register (see below).

- 2.) Read the three bytes that comprise the 24-bit value in the OL by reading the LSB first and the MSB last.

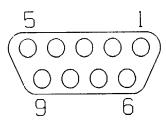

## 2.2.3 Writing the Command Register (CR)

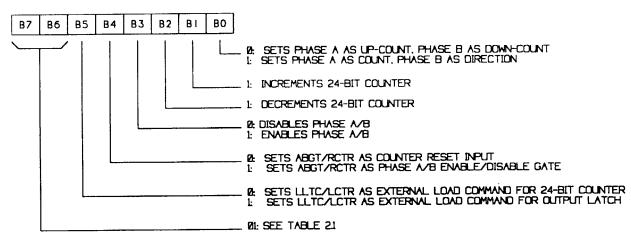

The CR is used to configure the counter for its various modes of operation. The following format is used for the command byte:

| Table 2.1 Register Select |    |                                        |

|---------------------------|----|----------------------------------------|

| B7                        | B6 | Register                               |

| 0                         | 0  | Master Control Register (MCR)          |

| 0                         | 1  | Input Control Register (ICR)           |

| 1                         | 0  | Output/Counter Control Register (OCCR) |

| 1                         | 1  | Quadrature Register (OR)               |

Mode bit selection for each control register is explained below.

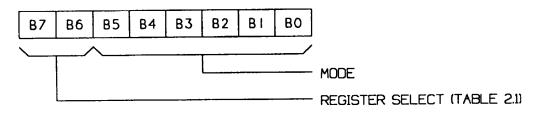

## 2.2.4 Master Control Register (MCR)

When enabling a value transfer from the PR to the counter (B3), the borrow toggle, the carry toggle, and the compare toggle flip-flops may be altered. You should read these values immediately after transfer and watch for a change in the desired status bit.

Note that a master reset overrides B1 and B3.

#### 2.2.5 Input Control Register (ICR)

When configured as up/down count mode (B0=0), the state of the unused input must be HIGH. In 6ther words, Phase A must be HIGH when Phase B is clocked LOW for input count, and Phase B must be HIGH when Phase A is clocked LOW for input count. Both phases are HIGH when no counts are input. It is illegal for both phases to be LOW at the same time.

In order to increment or decrement (by 1) the 24-bit counter by writing to the ICR, Phase A and Phase B signals must be HIGH at the same time.

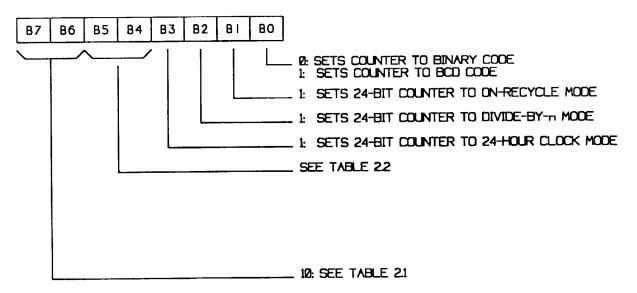

## 2.2.6 Output/Counter Control Register (OCCR)

| Table 2.2 Output/Counter Control Modes. |    |                                                    |  |

|-----------------------------------------|----|----------------------------------------------------|--|

| B5                                      | B4 | Mode                                               |  |

| 0                                       | 0  | Enable active LOW carry pulse, active LOW          |  |

|                                         |    | borrow on /CY and /BW, respectively                |  |

| 0                                       | 1  | Enable carry toggle flip-flop, borrow toggle flip- |  |

|                                         |    | flop on /CY and /BW, respectively                  |  |

| 1                                       | 0  | Enable active HIGH carry and borrow pulse on       |  |

|                                         |    | /CY and /BW, respectively                          |  |

| 1                                       | 1  | Enable comparator output on flip-flop and pulse    |  |

|                                         |    | on /BW                                             |  |

A forward slash (/) preceding a signal name denotes an active LOW signal.

On-recycle mode (B1) counts for only one cycle beginning with a counter reset or load command. It ends with the generation of a carry or a borrow. The counter is then inhibited until a new reset or load command is issued.

In divide-by-n mode (B2), the counter is reloaded with the Preset Register value every time the counter overflows or underflows. This feature is only valid in quadrature mode.

The 24-hour clock mode overrides both binary and BCD modes.

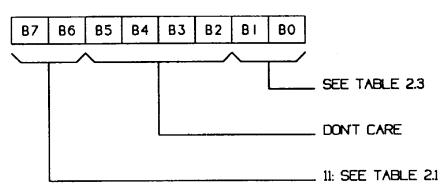

#### 2.2.7 Quadrature Register (OR)

| Table | Table 2.3 Quadrature Register Modes |                          |  |

|-------|-------------------------------------|--------------------------|--|

| B1    | B0                                  | Mode                     |  |

| 0     | 0                                   | Disables Quadrature Mode |  |

| 0     | 1                                   | 1x Quadrature Mode       |  |

| 1     | 0                                   | 2x Quadrature Mode       |  |

| 1     | 1                                   | 4x Quadrature Mode       |  |

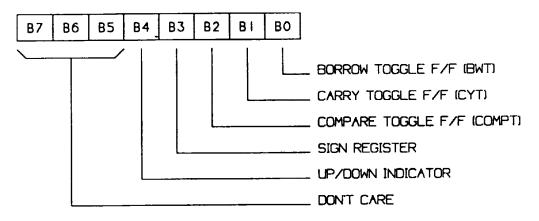

### 2.2.8 Output Status Register (OSR)

- **B0:** BWT This flip-flop changes state when the 24-bit counter underflows.

- **B1:** CYT This flip-flop changes state when the 24-bit counter overflows.

- **B2:** COMPT This flip-flop changes state when the 24-bit counter matches PR bits (0-2).

- **B3:** Sign Register This register bit is set when the 24-bit counter underflows indicating that a borrow has taken place. It is cleared when the 24-bit counter overflows indicating a carry. It is also reset whenever the 24-bit counter is reset.

- **B4:** Up/Down This bit set in quadrature mode indicates that the counter is operating in up-count mode. When clear, this bit indicates that the counter is in down-count mode. When not in quadrature mode, this bit is always set.

**B5-B7:** Don't care.

### 2.2.9 Typical Programming Examples Example 1

#### **Parameters:**

Quadrature mode. Index latches count in OL. BCD output.

#### Steps:

1.) Initialize the Counter

Write the following bytes to the CR:

| <u>Byte</u><br>35h | <u>Register</u><br>MCR | Description<br>Reset                                                                                         |

|--------------------|------------------------|--------------------------------------------------------------------------------------------------------------|

| 68h                | ICR                    | Sets the /LCTR - LLTC input to<br>latch the 24-bit counter value at the index<br>and enables Phases A and B. |

| 81h                | OCCR                   | Enables active LOW /CY and /BW and sets the counter to BCD mode.                                             |

| C3h                | QR                     | Enables quadrature decode mode.                                                                              |

2.) Read the Counter.

Write the following byte to the CR:

| <u>Byte</u> | <u>Register</u> | Description                                                                          |

|-------------|-----------------|--------------------------------------------------------------------------------------|

| 03h         | MCR             | Resets the PR and OL address counter and loads the OL with the 24-bit counter value. |

3.) Read the three bytes of data in the OL register (reading the LSB first and the MSB last) to obtain the 24-bit counter value.

#### Example 2

#### **Parameters:**

Count and direction mode. Reset counter on index. Binary output.

#### Steps:

1.) Initialize the Counter.

Write the following bytes to the CR:

| <u>Byte</u><br>35h | <u>Registers</u><br>MCR | Description<br>Reset                                                                                                               |

|--------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 49h                | ICR                     | Sets Phase A as count input and Phase B as direction input, enables Phases A and B, and sets /ABGT and /RCTR as the counter reset. |

| 80h                | 0CC                     | Enables active LOW /CY /and /BW and sets the counter to BCD mode.                                                                  |

| C0h                | QR                      | Disables quadrature decode mode.                                                                                                   |

2.) Read the Counter.

Write the following bytes to the CR:

| Byte | <u>Register</u> | Description |

|------|-----------------|-------------|

|------|-----------------|-------------|

03h MCR Resets the PR and OL address counter and loads the OL with the 24-bit counter value.

3.) Read the three bytes of data in the OL register (reading the LSB first and the MSB last) to obtain the 24-bit counter value.

#### Example 3

#### **Parameters:**

Value to be loaded in Counter: 654321h.

#### Steps:

1.) Reset the PR address.

| <u>Byte</u> | <u>Register</u> | <b>Description</b> |

|-------------|-----------------|--------------------|

| 01h         | MCR             | Reset PR address.  |

2.) Write the value to the PR.

| <u>Byte</u> | <u>Register</u> | <b>Description</b> |

|-------------|-----------------|--------------------|

| 21h         | Data            | LSB                |

| 43h         | Data            | LSB + 1            |

| 65h         | Data            | MSB                |

3.) Transfer PR to counter.

| Byte | Register | Description             |

|------|----------|-------------------------|

| 08h  | MCR      | Transfer PR to counter. |

### 2.2.10 Selecting A Sample Clock Frequency

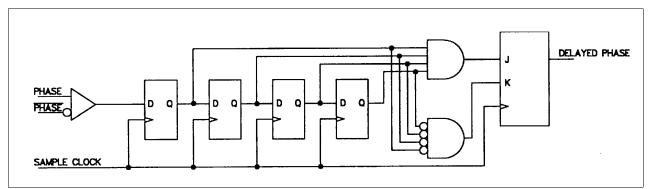

Each input line on the 5312B consists of a differential receiver pair followed by a 4-stage digital filter. This digital filter is shown in simplified form in figure 2.1, section 2.2.10. An input signal level must be a valid HIGH for four sample clock cycles or a valid LOW for four sample clock cycles before the filter output will change to the level of the input. This action prevents noise pulses of a duration shorter than (sample clock period)/4 from affecting the filter output signal.

To ensure that all valid input signals are transferred to the filter output, the sample clock period should be approximately one eighth the width of the narrowest positive or negative input pulse. In other words, the sample clock frequency should be eight times the input frequency assuming a 50 percent duty cycle input signal.

One side effect of the digital filter is a 4-sample period delay from the time a signal arrives at the input of the filter to the time it exits. For example, at the lowest sample clock frequency—625 KHz—the filter delay is approximately 8 microseconds. At the maximum recommended input pulse rate for this sample clock frequency, this is approximately 13 microseconds (assuming a 50 percent duty cycle).

Thus, the filter delay is approximately 60 percent of the minimum period input signal.

If delays of this length are unacceptable, a higher frequency sample clock may be used with the loss of some noise immunity.

For example, if you select a sample clock rate of 1.25 MHz, the filter delay is approximately 4 microseconds or one third of the input signal period. However, the noise immunity of the filter is

degraded when compared with that obtained at a clock frequency of 625 KHz. When using a clock period of 1.6 microseconds (1/0.625 MHz), intermittent noise pulses of greater than 6.4 microseconds will pass through the filter. Using a clock period of 0.8 microseconds (1/2.5 MHz), intermittent noise pulses of greater than 3.2 microseconds will pass through the filter.

Sample clock frequency selection is a trade-off between noise immunity and delay. For jumper options, see Section 1.

Figure 2.1 Example of a 4-stage signal conditioning filter.

A side effect of using a digital filter is a 4-sample propagation delay.

# **3 Interrupt Control**

## **3.1 Description of Interrupt Control**

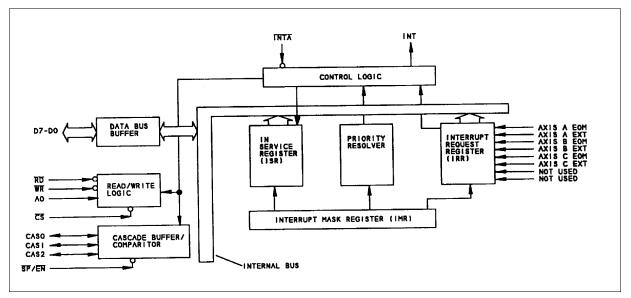

The 5312B uses an 8259A Programmable Interrupt Controller (PIC) to handle the interrupt sources on the board, and must be programmed prior to operation. Each axis can generate two interrupts: the first is a carry/borrow, signaling that an overflow or underflow has occurred, and the second interrupt is caused when a valid index pulse has occurred.

The PIC may only be used in a nonvectored mode (polled). When a board-level interrupt is generated, the PIC must be polled to determine which interrupt was triggered. The PIC may be disabled by removing jumper W8.

Only the features of the 8259A PIC that are used by 5312B are discussed below. For complete information on the 8259A *PIC* refer to the *Peripheral Components Manual* or the *Microsystem Components Handbook*, Vol 1, published by Intel.

Figure 3.1 shows a functional block diagram of the 8259A PlC. On the 5312B, the PlC is connected directly to the PC Bus through jumper W14.

Figure 3.1 PIC block level diagram.

The 5312B uses an Intel 8259A and is directly connected to the PC Bus through jumper W14.

#### 3.1.1 Interrupt Request Register (IRR), In-Service Register (ISR)

The interrupts at the interrupt request input lines (IR0-IR5) are handled by the IRR and the ISR. The IRR is used to store the interrupts requesting service, and the ISR is used to store the interrupts being serviced. Interrupts and IRR/ISR bits correspond to the format below.

#### 3.1.2 Priority Resolver (PR)

The Priority Resolver (PR) block determines the priority of the bits set in the IRR. The highest priority bit is selected and strobed into the corresponding ISR bit at the time of the poll command.

#### 3.1.3 Interrupt Mask Register (IMR)

The Interrupt Mask Register stores the bits that determine the interrupt lines to be masked. The IMR operates on the IRR. Masking a higher priority input will not affect the interrupt request lines of lower priority. Masking disables the interrupt for the masked input.

#### 3.1.4 Interrupt Output (INT)

The Interrupt Output (INT) signal indicates that the PIC has an interrupt request pending. This signal can be routed to PC Bus interrupt IRQ2 through IRQ7 (IRQ2 default) via W8. The poll command causes interrupt status to be placed on the bus during the next read of the PIC.

## 3.2 PIC Operation

#### 3.2.1 Interrupt Sequence, 80x86/80x88 Mode

The sequence of events during an interrupt when using an 80x86/80x88 CPU is as follows:

- 1.) One or more of the interrupt request lines (IR0-IR7) are raised high setting the corresponding IRR bit(s).

- 2.) The PIC evaluates these requests and sends an interrupt request to the CPU provided that jumper W8 is installed.

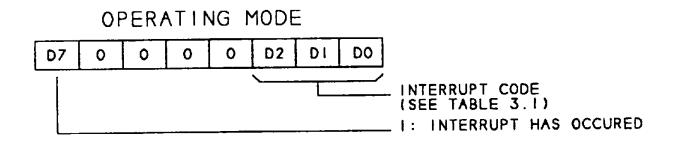

- 3.) The interrupt is acknowledged by your program interrupt service routine by writing a poll command (OCW3) to the PIC.

- 4.) The CPU reads the PIC to obtain the priority level as shown below. After the read, the high ISR bit is set, and the corresponding IRR bit is reset.

- 5.) The previous step completes the interrupt cycle. In the Automatic End-Of-Interrupt (AEOI) mode, the ISR bit is reset on the read following the poll command. Otherwise, the ISR bit remains set until an appropriate End-Of-Interrupt (EOI) command is issued.

**NOTE** If no lines are HIGH at step 4 of the sequence (i.e., the IR line went HIGH to generate an interrupt request but then went away before it was acknowledged), the PIC will issue an interrupt level 7. This causes the call address or the vector byte to look as if IR7 generated an interrupt request occurred or a noise spike tripped the request line.

| Table | 9.1 | nterr | upt Code.         |

|-------|-----|-------|-------------------|

| D2    | D1  | D0    | Interrupt Request |

| 0     | 0   | 0     | IRQ0              |

| 0     | 0   | 1     | IRQ1              |

| 0     | 1   | 0     | IRQ2              |

| 0     | 1   | 1     | IRQ3              |

| 1     | 0   | 0     | IRQ4              |

| 1     | 0   | 1     | IRQ5              |

| 1     | 1   | 0     | IRQ6              |

| 1     | 1   | 1     | IRQ7              |

The interrupt code returns the highest priority interrupt and sets the corresponding ISR bit.

#### 3.2.2 End-of-Interrupt Command

After the priority level is read, the ISR bit must be reset. This is done with EOI command from the host PC, or it can be done automatically in the AEOI mode. There are two forms of the EOI command—Specific and Non-Specific. A Non-Specific EOI command resets the highest ISR bit of those that were set, and a Specific EOI command can be issued to reset a specified ISR bit.

#### 3.2.3 Completing an Interrupt

You have to provide an interrupt routine to trap IR7 interrupt glitches that appear as interrupt 7 requests. In the AEOI mode, the ISR bit for the interrupt being serviced is reset automatically at the interrupt return in your interrupt routine.

### **3.3 Operating Modes** 3.3.1 Fully Nested Mode

This is the default mode entered after initialization unless another mode is programmed. In this mode, interrupt requests are ordered in priority from 0 through 7 with 0 being the highest priority. When a poll command is received and the priority level is read, the highest priority request is placed on the data bus. The corresponding bit in the ISR is also set. It stays set until the CPU issues an EOI command, or, if in AEOI mode, until the priority level is read. While the ISR bit is set, all further interrupts of equal or lower priority are inhibited. Interrupts of higher priority will issue an interrupt request (which will be acknowledged only if the PC has unmasked the interrupt).

#### 3.3.2 Special Mask Mode

This mode is similar to the fully nested mode except that when a bit in the ISR is set, it only inhibits interrupt requests at that level. All other unmasked interrupt requests (lower as well as higher) are enabled.

### 3.3.3 Specific Rotation (Specific Priority)

The default priority of interrupts is IR0 (highest) through IR7 (lowest). This can be changed using the set priority command. This command specifies one input as having the lowest priority and fixing all other priorities. For example, if IR2 is specified as having the lowest priority, the priority of interrupts will be: IR3 (highest), IR4, IR5, IR6, IR7, IR0, IR1, IR2 (lowest).

### 3.3.4 Automatic Rotation (Equal Priority)

In this mode, a device, after being serviced, receives the lowest priority. Such a device requesting an interrupt would have to wait until all other devices have been serviced.

### 3.3.5 Non-Vectored Mode (Poll Command)

The PIC must be polled for interrupt status. To do this, the poll command is written to the PIC, and then the status is read. The PIC treats the read pulse as an INTA pulse. The interrupt is frozen from the write to the read.

## 3.4 PIC Programming

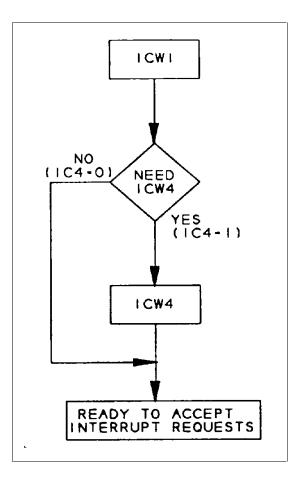

The PIC accepts two types of command words from the CPU—Initialization Command Words (ICW) and Operational Command Words (OCW).

## 3.4.1 Initialization Command Words (ICW)

Figure 3.2 PIC initialization sequence.

Bit D4 set assumes the next word issued will be ICW4.

Before normal operation can begin, the PIC must be brought to a starting point by a sequence of three bytes. Figure 3.2 shows the initialization sequence. Whenever a command is written to the PIC low port with bit D4 = 1, it is interpreted as ICW1. Register ICW1 starts the initialization sequence during which the following automatically occur:

1.) The IMR is cleared.

- 2.) IR7 is assigned the lowest priority.

- 3.) The slave mode address is set to 7.